**Application Note**

September 2002

AN1038

#### Introduction

The ISL55185XEVAL1 board can be used to evaluate the new ISL5585 3.3volt SLIC. This platform supports the evaluation of the performance of the ISL5585 at 3.3 volts with a 5 volt CODEC. The lab data presented in this application note had the following supplies voltages: Vcc (ISL5585) = 3.3V, Vcc (CODEC) = 5V, VBH = -100v and Vbl = -24v.

The ISL5585XEVAL1 evaluation board provides a complete evaluation system for the ISL5585 family of ringing SLICs. Included on the evaluation board is a single +5V CODEC for line circuit evaluations and on board logic for stand alone operation. The evaluation boards have been designed to support back to back operation, providing further insight to the complete signal path and solution.

The transient behavior of the ISL5585 in response to mode changes has been improved. The benefit to the application is reduction or more likely elimination of  $\overline{\text{DET}}$  glitches when off hook events occur.

Voltage ratings for external components have been selected based on 100V device operation, therefore compatibility to lower voltage versions is guaranteed.

### **Getting Started**

Your evaluation kit should contain application note AN1038 and the following hardware.

- 1. One ISL5585XEVAL1evaluation board.

- 2. One ISL5585X device sample, already in board.

- 3. One PLCC extraction tool.

- 4. One cable assembly with multi colored conductors.

- 5. One cable assembly with solid white conductors.

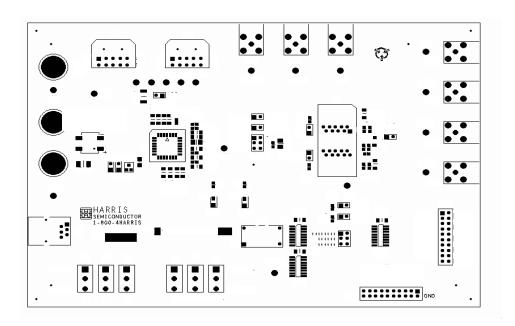

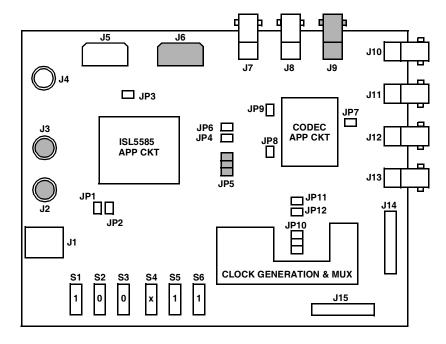

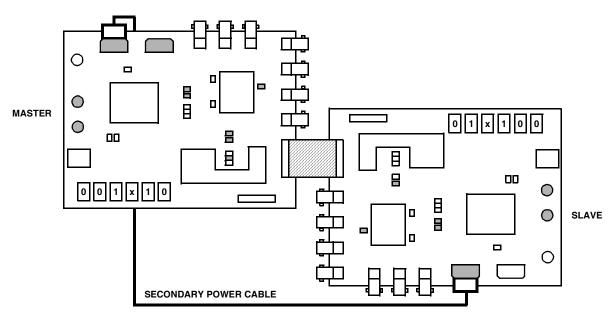

The evaluation board should have the same appearance as the silk screen shown in Figure 1.

### Applying Power to the Evaluation Board

Here are a few safeguards with power sequencing until you are accustomed to using the high voltages required by the devices.

- 1. Limit the current on all power supplies to 100mA.

- 2. Turn on the power supplies after the power cables are attached to the evaluation boards.

FIGURE 1. EVALUATION BOARD SILK SCREEN

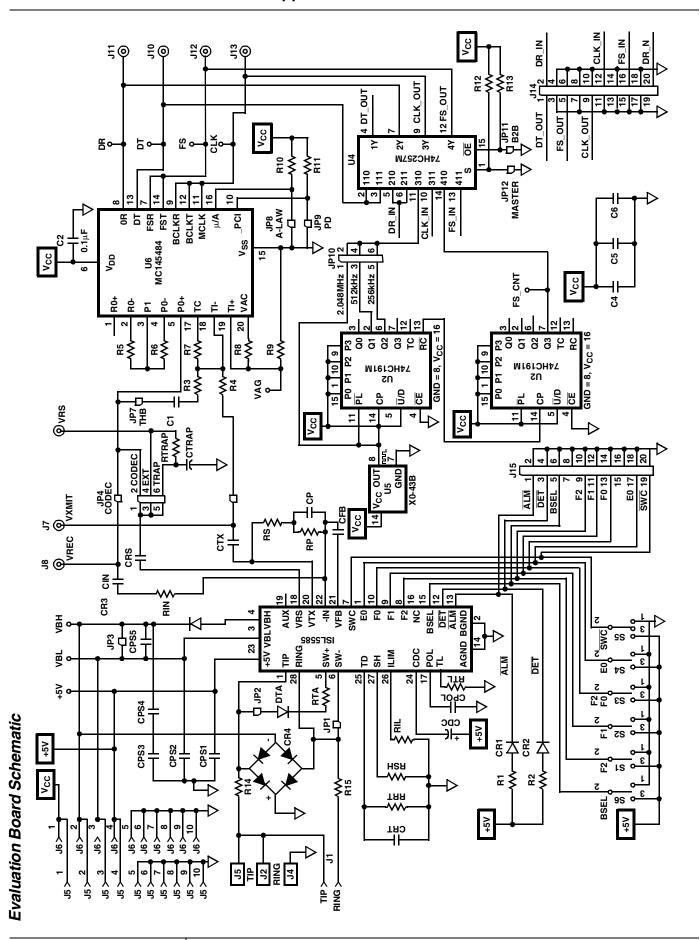

# **Evaluation Board Functional Description**

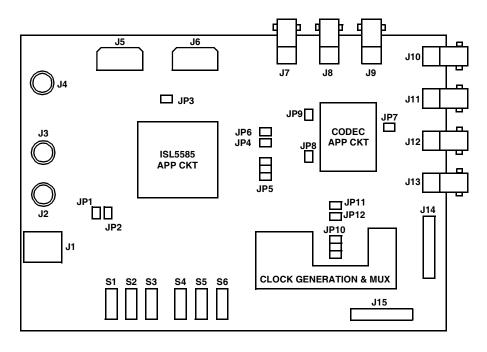

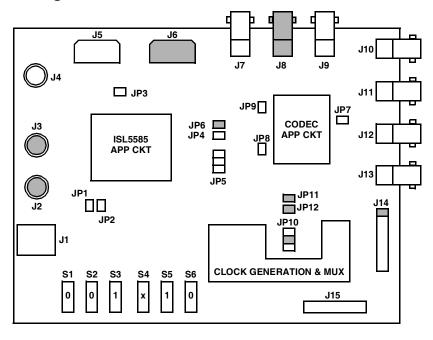

FIGURE 2. EVALUATION BOARD FUNCTIONAL DIAGRAM

# **Evaluation Board Jumper Definitions**

| JUMPER | DESCRIPTION                                                                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1    | Connects SW- directly to the device Ring terminal of device. Used in conjunction with external load D <sub>TA</sub> and R <sub>TA</sub> .                                                                                            |

| JP2    | Connects SW+ through test load to the Tip terminal of device. Used in conjunction with external load D <sub>TA</sub> and R <sub>TA</sub> .                                                                                           |

| JP3    | Not used. Leave open.                                                                                                                                                                                                                |

| JP4    | Connects the receive output of the CODEC (U6) to the device receive input -IN. Path is AC coupled with CIN.                                                                                                                          |

| JP5    | Position1, CODEC: Connects the CODEC receive output to the device ringing input. Path is AC coupled by C <sub>RS</sub> .                                                                                                             |

|        | Position 2, EXT: Connects the VRS connector J9 to the device ringing input. Path is AC coupled by C <sub>RS</sub> .                                                                                                                  |

|        | Position 3 TRAP: Connects the VRS connector J9 thru RC network to the device ringing input. Path is AC coupled.                                                                                                                      |

| JP6    | Connects the device transmit output VTX to the CODEC amplifier for transhybrid balance. Path is AC coupled by C <sub>TX</sub> .                                                                                                      |

| JP7    | Connects the receive output of CODEC to transhybrid amplifier, AC coupled by C <sub>1</sub> . Normally inserted for proper operation.                                                                                                |

| JP8    | Inserting jumper sets the CODEC to A-law coding. Open sets the CODEC to μ-law coding.                                                                                                                                                |

| JP9    | Inserting jumper powers down the CODEC. Open provides normal CODEC operation.                                                                                                                                                        |

| JP10   | Position 1: Sets the CODEC master clock to 2.048MHz.                                                                                                                                                                                 |

|        | Position 2: Sets the CODEC master clock to 512kHz                                                                                                                                                                                    |

|        | Position 3: Sets the CODEC master clock to 256kHz.                                                                                                                                                                                   |

| JP11   | Enables the on board logic multiplexer. Should be installed for single board or back to back evaluations. Remove when driving BNCs J10 thru J13.                                                                                     |

| JP12   | Inserting jumper selects on board clock and frame sync generator. Insert to configure board as master for back to back evaluations or for single board evaluations. Remove to configure board as slave for back to back evaluations. |

#### **Test Points**

Each connector interface to the evaluation board has a test point. All test points are DC coupled and should be guarded against ground shorts. High impedance test inputs, such as oscilloscopes or DVMs, should be used to monitor these points. Unused BNC connections also provide convenient test point access.

#### **Toggle Switches**

The six toggle switches, S1 thru S6, interface directly to the ISL5585 device. Positioning any switch towards the top of the board is a logic "1". Positioning any switch towards the bottom of the board is a logic "0". All switches are labeled with the control signal names.

The switch E0 selects the switch hook (E0 = 1) or the ground key detector (E0 = 0) to appear at  $\overline{DET}$ . During ringing, the device overrides E0 and sends the ring trip detector to  $\overline{DET}$ . The switched labeled  $\overline{SWC}$  turns on the uncommitted switch when set to a logic low. The battery select signal BSEL, selects the high battery when set to logic high. The operating modes for the ISL5585 device are provided in Table 1.

**TABLE 1. ISL5585 OPERATING MODES**

| OPERATING MODE           | F2 | F1 | F0 |

|--------------------------|----|----|----|

| Low Power Standby        | 0  | 0  | 0  |

| Forward Active           | 0  | 0  | 1  |

| Unused                   | 0  | 1  | 0  |

| Reverse Active           | 0  | 1  | 1  |

| Ringing                  | 1  | 0  | 0  |

| Forward Loop Back (Note) | 1  | 0  | 1  |

| Tip Open                 | 1  | 1  | 0  |

| Power Denial             | 1  | 1  | 1  |

NOTE: The ISL5585 device should always operate from low battery voltage when using the Forward Loop Back mode.

Refer to the device electrical data sheet for detailed descriptions regarding each operating mode according to the device under evaluation.

### **Evaluation Board Connector Descriptions**

| CONNECTOR | DESCRIPTION                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| J1        | RJ11 type phone connector.                                                                                            |

| J2        | Ring terminal of board.                                                                                               |

| J3        | Tip terminal of board.                                                                                                |

| J4        | Grounding lug connected to board ground plane.                                                                        |

| J5        | 1: V <sub>CC</sub> . Positive 5V supply to CODEC U6, clock generator U5 and logic devices U2 thru U4 (red wire).      |

|           | 2: V <sub>BH</sub> . High negative battery supply to the ISL5585 device (orange wire).                                |

|           | 3: V <sub>BL</sub> . Low negative battery supply to the ISL5585 device (yellow wire).                                 |

|           | 4: +5V. Positive 5V supply to the ISL5585 device and LEDs (green wire).                                               |

|           | 7 thru 10: GND. Twisted pair returns for external supply connections (black wires).                                   |

| J6        | Identical pinout as J5. Either connector provides daisy chain connection to second board for back to back evaluation. |

| J7        | Transmit analog output from ISL5585 device, VTX. This path is AC coupled by C <sub>TX</sub> .                         |

| J8        | Receive analog input to ISL5585 device, VREC. This path is AC coupled by C <sub>IN</sub> .                            |

| J9        | Ringing input to ISL5585 device, VRS. This path is AC coupled by C <sub>RS</sub> .                                    |

| J10       | Serial transmit data output of CODEC U6.                                                                              |

| J11       | Serial receive data input to CODEC U6.                                                                                |

| J12       | Common frame sync input for receive and transmit digital data.                                                        |

| J13       | Common clock for CODEC data transfer and conversion.                                                                  |

| J14       | 20 pin, 100 mil spacing header with all digital PCM data interfaces to CODEC U6.                                      |

| J15       | 20 pin, 100 mil spacing header with all digital interfaces to ISL5585 device.                                         |

## Stand Alone Configuration

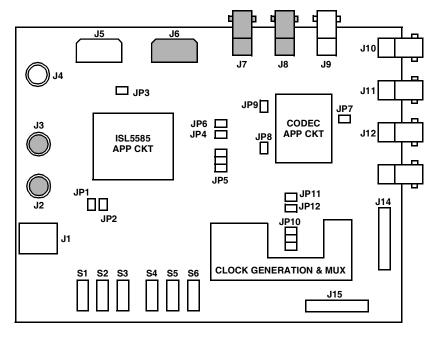

FIGURE 3. STAND ALONE CONNECTORS AND JUMPERS

#### Description

The standalone configuration supports any measurement of the ISL5585 device. With all the jumper locations open, the device is totally isolated from all other active circuitry on the evaluation board. All other circuitry is powered, but does not interfere with proper SLIC operation.

#### Power Supply Connections

Power should be applied to the evaluation board using the primary power cable. Either J5 or J6 may be used. Prior to applying power, the voltage setting of each supply should be verified. The power supplies should be turned off while mating the primary power cable to the evaluation board.

#### Jumper Settings

All jumper positions should be open for the stand alone configuration.

#### Measurement Capability

Nearly all AC and DC parameters of the device can be measured using this configuration. The device has been socketed to allow easy measurements of more than a single device. An extraction tool has been included with the evaluation kit and should be used to remove the device from the socket. The typical device measurements are listed below.

- 1. Power supply current per operating mode.

- 2. Tip and Ring DC voltages per operating mode.

- 3. On hook AC gains  $G_{42}$ ,  $G_{24}$  and  $G_{44}$ .

- 4. Off hook AC gains  $G_{42}$ ,  $G_{24}$  and  $G_{44}$ .

- 5. Other AC parameters such as longitudinal balance.

#### Status LEDs

The status LEDs DET and ALM are active for the stand alone configuration. DET should only light when a DC current path exists from Tip to Ring or during forward loop back. ALM should only light during forward loop back operation. Normal device evaluations should not cause the ALM indicator to light.

#### **Uncommitted Switch Jumpers**

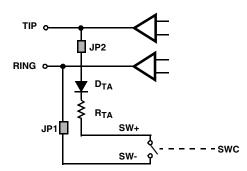

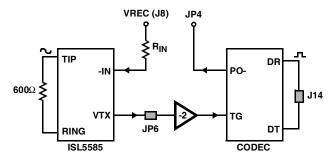

When the jumpers JP1 and JP2 are installed, the uncommitted switch is connected across Tip and Ring. The test load of  $D_{TA}$  and  $R_{TA}$  will connect across the Tip and Ring terminals when the uncommitted switch is turned on. The DC load will result in  $\overline{DET}$  transitioning to a logic low. The circuit diagram is shown below.

FIGURE 4. TEST LOAD SWITCHING

#### Socket Removal

The surface mount socket for the ISL5585 device has the same solder foot print as the PLCC package. Therefore, the socket may be removed for more extensive characterization.

# Stand Alone Configuration Typical Measurements

## Supply Currents (milli amps) - On Hook

| OPERATING MODE    | F2, F1, F0 | E0  | swc | BSEL | ICC<br>(Vcc= 3.3v) | IBH<br>(Vbh= -100v) | IBL<br>(Vbl = -24v) |

|-------------------|------------|-----|-----|------|--------------------|---------------------|---------------------|

| Low Power Standby | 0, 0, 0    | х   | 1   | 1    | 2.9                | 0.6                 | 0.3                 |

| Forward Active    | 0, 0, 1    | х   | 1   | 0    | 3.7                | 0                   | 1.2                 |

| Unused            | 0, 1, 0    | n/a | n/a | n/a  | n/a                | n/a                 | n/a                 |

| Reverse Active    | 0, 1, 1    | х   | 1   | 0    | 3.7                | 0                   | 1.2                 |

| Ringing           | 1, 0, 0    | х   | 1   | 1    | 5.6                | 1.5                 | 0.7                 |

| Forward Loop Back | 1, 0, 1    | х   | 1   | 0    | 11.9               | 0                   | 20                  |

| Tip Open          | 1, 1, 0    | x   | 1   | 1    | 2.9                | 0.6                 | 0.3                 |

| Power Denial      | 1, 1, 1    | х   | 1   | х    | 3.3                | 0                   | 0.2                 |

## Tip and Ring Voltages (Volts) - On Hook

| OPERATING MODE    | F2, F1, F0 | E0  | swc | BSEL | TIP   | RING  |

|-------------------|------------|-----|-----|------|-------|-------|

| Low Power Standby | 0, 0, 0    | х   | 1   | 1    | -0.7  | -52   |

| Forward Active    | 0, 0, 1    | х   | 1   | 0    | -3.9  | -17   |

| Unused            | 0, 1, 0    | n/a | n/a | n/a  | n/a   | n/a   |

| Reverse Active    | 0, 1, 1    | х   | 1   | 0    | -17   | -3.9  |

| Ringing           | 1, 0, 0    | х   | 1   | 1    | -50   | -50   |

| Forward Loop Back | 1, 0, 1    | х   | 1   | 0    | -3.9  | -17   |

| Tip Open          | 1, 1, 0    | х   | 1   | 1    | Float | -52   |

| Power Denial      | 1, 1, 1    | х   | 1   | х    | Float | Float |

## AC Gains (dB), Off Hook, $600\Omega$ Termination - Forward and Reverse Active Only

| OPERATING MODE    | F2, F1, F0                                                                                                                                        | E0              | swc                        | BSEL                                                                      | G <sub>42</sub>                        | G <sub>24</sub> | G <sub>44</sub> |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------|---------------------------------------------------------------------------|----------------------------------------|-----------------|-----------------|--|

| Forward Active    | 0, 0, 1                                                                                                                                           | х               | 1                          | 0                                                                         | 0.0                                    | -7.3            | -7.3            |  |

| Reverse Active    | 0, 1, 1                                                                                                                                           | х               | 1                          | 0                                                                         | 0.0                                    | -7.3            | -7.3            |  |

| AC Gain Equations |                                                                                                                                                   | G <sub>42</sub> |                            |                                                                           |                                        |                 |                 |  |

|                   | $G_{4-2} = \frac{V_{2W}}{V_{1N}} = 2\left(\frac{R_S}{R_{1N}}\right) \frac{Z_L}{Z_L + Z_O + 2_{RP}} = 2\frac{Z_L}{Z_L + Z_L} = \frac{R_S}{R_{1N}}$ |                 |                            |                                                                           |                                        |                 |                 |  |

|                   | G <sub>24</sub>                                                                                                                                   |                 |                            |                                                                           |                                        |                 |                 |  |

|                   | $G_{24} = -\left(\frac{Z_{O}}{Z_{O} + 2R_{P} + Z_{L}}\right)$                                                                                     |                 |                            |                                                                           |                                        |                 |                 |  |

|                   | G <sub>44</sub>                                                                                                                                   |                 |                            |                                                                           |                                        |                 |                 |  |

|                   |                                                                                                                                                   |                 | $G_{44} = G_{42} \times G$ | $\hat{A}_{24} = -\left(\frac{R_S}{R_{IN}}\right)\left(\frac{1}{2}\right)$ | $\frac{Z_{O}}{Z_{L} + 2R_{P} + Z_{O}}$ |                 |                 |  |

## Ringing Configuration

FIGURE 5. RINGING CONNECTORS AND JUMPERS

#### Description

The ringing configuration supports full evaluation of the ringing capability of the ISL5585 device. The evaluation board design does not include a 20Hz digital code generator, therefore, all ringing waveforms will be sourced by external test equipment.

#### **Power Supply Connections**

Power should be applied to the evaluation board using the primary power cable. Either J5 or J6 may be used. Prior to applying power, the voltage setting of each supply should be verified. The power supplies should be turned off while mating the primary power cable to the evaluation board.

#### Jumper Settings

The jumper JP5 provides three positions for different ringing techniques.

**TABLE 2. JP5 JUMPER POSITIONS**

| JP5 POSN | DESCRIPTION                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------|

| CODEC    | Connects the CODEC receive output to the device ringing input. Signal path is AC coupled.             |

| EXT      | Connects the VRS connector J9 to the device ringing input. Signal path is AC coupled.                 |

| TRAP     | Connects the VRS connector J9 thru RC network to the device ringing input. Signal path is AC coupled. |

#### **CODEC Ringing**

Most test equipment designed to evaluate the CODEC PCM interface are capable of output frequencies as low as 20Hz. If such a piece of equipment is available, then CODEC

ringing can be evaluated. The digital interface to the CODEC would be provided by the BNC connectors J10 thru J13. Verify JP11 is open prior to driving signals into the BNC connectors. An output level of 0dBm from the CODEC will provide full scale ringing when operating from -100V battery.

#### External Ringing Source

Using an external function generator at J9 provides the most control of the ringing waveform. The flexibility of the ringing interface can be fully exercised by the function generator. To evaluate DC offsets during ringing, the capacitor C<sub>RS</sub> must be shorted. Most functions generators provide DC offset as part of the output waveform. Positive DC offsets on VRS move Tip towards ground and Ring towards battery.

#### Trapezoidal Ringing

A logic level square wave, at J9, with 50% duty cycle will be shaped by the components  $R_{TRAP}$  and  $C_{TRAP}$  when this jumper position is selected. The components shipped with the evaluation board will result in a 75 $V_{RMS}$  trapezoidal ringing waveform when operating from a -100V battery.

#### Ring Trip Control

Three very distinct actions occur when the devices detects a ring trip. First, the  $\overline{\text{DET}}$  output is latched low. The latching mechanism eliminates the need for software filtering of the detector output. The latch is cleared when the operating mode is changed externally. Second, the VRS input is disabled, removing the ring signal from the line. Third, the device is internally forced to the forward active mode. The low battery is not automatically selected upon ring trip.

## Digital Loop Back Configuration

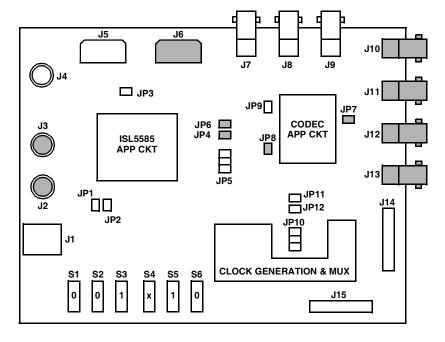

FIGURE 6. DIGITAL LOOP BACK CONNECTORS AND JUMPERS

#### Description

The digital loop back configuration verifies the interface and operation of the ISL5585 device and the CODEC. This configuration provides a self test to verify proper operation of the board. In addition, it provides a complete digital loop, allowing analog control of the digital input and output of the CODEC. Forward active and reverse active or teletax will support the digital loop back configuration.

### **Power Supply Connections**

Power should be applied to the evaluation board using the primary power cable. Either J5 or J6 may be used. Prior to applying power, the voltage setting of each supply should be verified. The power supplies should be turned off while mating the primary power cable to the evaluation board.

#### Jumper Settings

All jumper settings and functions are described below.

TABLE 3. DIGITAL LOOP BACK JUMPER POSITIONS

| JUMPER       | DESCRIPTION                                                                             |

|--------------|-----------------------------------------------------------------------------------------|

| JP6          | Connects the device transmit output VTX to the CODEC amplifier for transhybrid balance. |

| JP10, POSN 2 | Sets the CODEC master clock to 512kHz.                                                  |

| JP11         | Enables the on board logic multiplexer.                                                 |

| JP12         | Inserting jumper selects on board clock and frame sync generator.                       |

| J14, POSN 1  | Connects the CODEC digital output DT to digital input DR.                               |

#### Signal Flow

Driving a signal at VREC, J8, will result in a signal from the CODEC receive output when the ISL5585 device is terminated at Tip and Ring. The following diagram shows the signal path formed by the jumpers and terminated SLIC.

FIGURE 7. DIGITAL LOOP BACK SIGNAL FLOW

With VREC input signal level of  $0.775V_{RMS}$ , a signal level of  $0.337V_{RMS}$  should result at the VTX output when terminated with  $600\Omega$ . The signal level at VTX is determined by the 4-wire to 4-wire gain,  $G_{44}$ , of the ISL5585. The transhybrid balance is not connected, therefore, the digitized signal level at the CODEC will be approximately  $0.674V_{RMS}$ . The CODEC transfer functions are set for unity gain, therefore the signal level at PO- should be approximately  $0.674V_{RMS}$ .

The signal levels for digital loop back are independent of the clock selected by JP10.

Refer to the device electrical data sheet for the design equations for the 4-wire to 4-wire gain as a function of termination and synthesized impedance.

## **PCM4 Configuration**

FIGURE 8. PCM4 CONNECTORS AND JUMPERS

#### Description

The PCM4 configuration verifies the AC transmission of the ISL5585 and CODEC. Any piece of test equipment capable of PCM testing with digital and analog interfaces can be used in this configuration.

#### Power Supply Connections

Power should be applied to the evaluation board using the primary power cable. Either J5 or J6 may be used. Prior to applying power, the voltage setting of each supply should be verified. The power supplies should be turned off while mating the primary power cable to the evaluation board.

#### Jumper Settings

All jumper settings are described below.

**TABLE 4. PCM4 JUMPER POSITIONS**

| JUMPER | DESCRIPTION                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP4    | Connects the receive output of the CODEC (U6) to the device receive input -IN through R <sub>IN</sub> . Signal path is AC coupled.                               |

| JP6    | Connects the device transmit output VTX to the CODEC amplifier for transhybrid balance. Signal path is AC coupled.                                               |

| JP7    | Connects the receive output of CODEC to transhybrid amplifier, AC coupled by C1.                                                                                 |

| JP8    | Inserting jumper set the CODEC to A-law coding. Open sets the CODEC to $\mu$ -law coding. This must match PCM test equipment coding scheme for proper operation. |

### Clock and Frame Sync

The clock and frame sync signals are driven at connectors J13 and J12 respectively. The clock input is common to the MCLK, BCLKT and BCLKR of the CODEC. The frame sync input is common to the receive and transmit frame syncs, FSR and FST, of the CODEC. These connections define synchronous mode of operation.

#### Digital to Analog

The receive signal path is defined from the CODEC PCM input to the ISL5585 Tip and Ring outputs. The PCM4 tester is capable of driving digital test signals on the PCM bus and measuring the resultant signal at Tip and Ring. With this type of capability, the full receive path can be evaluated. Typical performance measurements include overall loss, gain variation versus frequency, gain versus signal level and 2-wire return loss. In addition fidelity measurements such as idle channel noise and distortion are also performed.

#### Analog to Digital

The transmit signal path is defined from ISL5585 Tip and Ring interface to the CODEC PCM output. The same tests performed for the receive path also apply to the transmit path.

#### Digital to Digital

The digital to digital path is from the CODEC PCM input to the CODEC PCM output. This signal path provides a measure of the transhybrid balance for the line circuit. Most other AC performance metrics are base on analog to digital or digital to analog measurements. For proper transhybrid measurements, verify jumper JP7 is inserted.

## PCM4 Configuration Typical Measurements

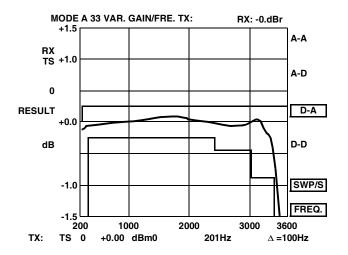

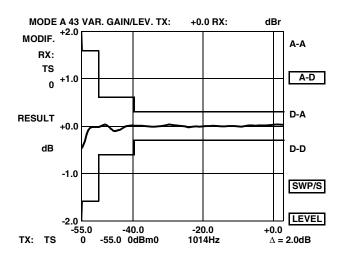

FIGURE 9. DIGITAL TO ANALOG GAIN vs FREQUENCY

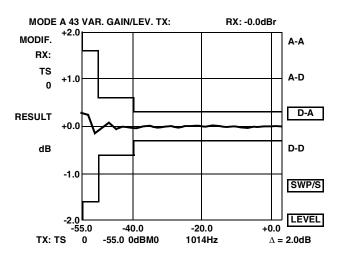

FIGURE 11. DIGITAL TO ANALOG GAIN vs LEVEL

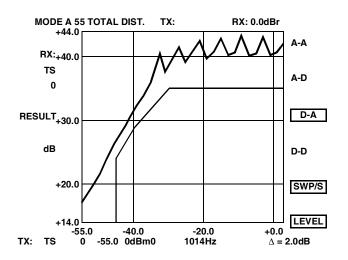

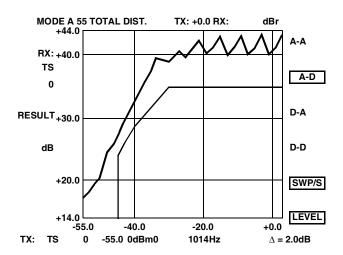

FIGURE 13. DIGITAL TO ANALOG TOTAL DISTORTION

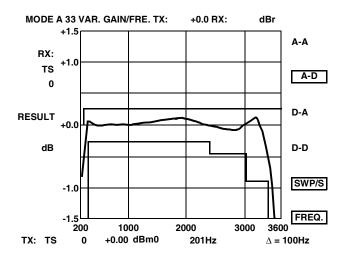

FIGURE 10. ANALOG TO DIGITAL GAIN vs FREQUENCY

FIGURE 12. ANALOG TO DIGITAL GAIN vs LEVEL

FIGURE 14. ANALOG TO DIGITAL TOTAL DISTORTION

## Back to Back Configuration

FIGURE 15. BACK TO BACK CONNECTORS AND JUMPERS

#### Description

The back to back configuration connects two evaluation boards together at the PCM interface. The PCM output data from one board is the PCM input data to the other board. One board is configured as a master for clock generation and the other is configured as a slave. A secondary power cable provides daisy chain power to the second evaluation board.

#### **Power Supply Connections**

Power should be applied to the evaluation board using the primary power cable. Either J5 or J6 may be used. Prior to applying power, the voltage setting of each supply should be verified. The power supplies should be turned off while mating the power cables to the evaluation boards.

#### Jumper Settings

All jumper settings are described below.

**TABLE 5. MASTER BOARD JUMPER POSITIONS**

| JUMPER       | DESCRIPTION                                                                                                         |  |

|--------------|---------------------------------------------------------------------------------------------------------------------|--|

| JP4          | Connects the receive output of the CODEC (U6) to the device receive input -IN through $R_{\mbox{\scriptsize IN}}$ . |  |

| JP6          | Connects the device transmit output VTX to the CODEC amplifier for transhybrid balance.                             |  |

| JP7          | Connects the receive output of CODEC to transhybrid amplifier, AC coupled by C1.                                    |  |

| JP10, POSN 2 | Sets the CODEC master clock to 512kHz.                                                                              |  |

| JP11         | Enables the on board logic multiplexer.                                                                             |  |

| JP12         | Configures board as master.                                                                                         |  |

TABLE 6. SLAVE BOARD JUMPER POSITIONS

| JUMPER | DESCRIPTION                                                                                          |

|--------|------------------------------------------------------------------------------------------------------|

| JP4    | Connects the receive output of the CODEC (U6) to the device receive input -IN through $R_{\rm IN}$ . |

| JP6    | Connects the device transmit output VTX to the CODEC amplifier for transhybrid balance.              |

| JP7    | Connects the receive output of CODEC to transhybrid amplifier, AC coupled by C1.                     |

| JP11   | Enables the on board logic multiplexer.                                                              |

In this configuration the master board provides the clock and frame sync to the slave board. The selection of the clock rate is arbitrary and may be any of the available frequencies.

The ribbon cable used to connect the two boards at J14 also connects the ground planes of the two evaluation boards. Having returns adjacent to the high speed clock edges is critical to reducing board level noise.

If transmission quality is poor verify both master and slave boards are set up for same coding scheme, JP8. In addition, verify the transhybrid jumper, JP7, is inserted in both boards. If signal quality still does not improve, verify JP12 of the slave board is not populated.

#### Analog to Analog Verification

The back to back configuration verifies the complete signal path of two evaluation boards. Full duplex transmission is provided from one Tip and Ring interface to the other. Both ISL5585 devices do not have to be in the same transmission mode (forward, reverse or teletax) for proper back to back operation.

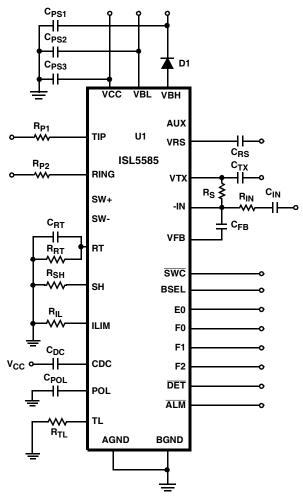

FIGURE 16. ISL5585 BASIC APPLICATION CIRCUIT

# **Basic Application Circuit Component List**

| COMPONENT                                                                                   | VALUE   | TOLERANCE | RATING | COMPONENT                                           | VALUE                                           | TOLERANCE | RATING |  |

|---------------------------------------------------------------------------------------------|---------|-----------|--------|-----------------------------------------------------|-------------------------------------------------|-----------|--------|--|

| U1 - Ringing SLIC                                                                           | ISL5585 | N/A       | N/A    | C <sub>DC</sub> , C <sub>FB</sub>                   | 4.7μF                                           | 20%       | 10V    |  |

| R <sub>RT</sub>                                                                             | 20kΩ    | 1%        | 0.1W   | C <sub>PS1</sub>                                    | 0.1μF                                           | 20%       | >100V  |  |

| R <sub>SH</sub>                                                                             | 49.9kΩ  | 1%        | 0.1W   | C <sub>PS2</sub> , C <sub>PS3</sub>                 | 0.1μF                                           | 20%       | 100V   |  |

| R <sub>IL</sub>                                                                             | 71.5kΩ  | 1%        | 0.1W   | D <sub>1</sub>                                      | 1N400X type with breakdown > 100V.              |           | 100V.  |  |

| R <sub>S</sub>                                                                              | 66.5kΩ  | 1%        | 0.1W   | $R_{P1}, R_{P2} = 50\Omega,$                        | Protection resistor values are application      |           | •      |  |

| R <sub>TL</sub>                                                                             | 17.8kΩ  | 1%        | 0.1W   | 0.5W, dependent and will be protection requirement: |                                                 |           | ,      |  |

| C <sub>IN</sub> , C <sub>RS</sub> , C <sub>TX</sub> , C <sub>RT</sub> ,<br>C <sub>POL</sub> | 0.47μF  | 20%       | 10V    |                                                     | applications will use $\geq 50\Omega$ per side. |           |        |  |

**Design Parameters**: Ring Trip Threshold =  $90mA_{PEAK}$ . Switch Hook Threshold = 12mA, Loop Current Limit = 24.6mA, Transient current limit:  $I_{SOURCE} = 100mA$ ,  $I_{SINK} = 120mA$ , Synthesize Device Impedance =  $66.5K\Omega/133.3 = 500\Omega$ , with  $51\Omega$  protection resistors, impedance across Tip and Ring terminals =  $603\Omega$ .

### **Application Note 1038**

## ISL5585XEVAL1 Electrical Component List

| COMPONENT                           | VALUE      | TOLERANCE | RATING | COMPONENT                                              | VALUE       | TOLERANCE                 | RATING |

|-------------------------------------|------------|-----------|--------|--------------------------------------------------------|-------------|---------------------------|--------|

| U <sub>1</sub> - Ringing SLIC       | HC5518x    | N/A       | N/A    | R <sub>3</sub> , R <sub>7</sub>                        | 100kΩ       | 1%                        | 0.10W  |

| U <sub>2</sub> , U <sub>3</sub>     | 74HC191M   | N/A       | N/A    | R5, R6, R8, R9,<br>R10, R11, R12,<br>R13               | 10kΩ        | 1%                        | 0.10W  |

| U <sub>4</sub>                      | 74HC257M   | N/A       | N/A    | R14, R15                                               | 51Ω         | 5%, picked to $0.1\Omega$ | 0.50W  |

| U <sub>5</sub>                      | XO-43B     | N/A       | N/A    | CRT, C <sub>IN</sub> , CRS,<br>CTX, C1, CPOL,<br>CTRAP | 0.47μF      | 20%                       | 20V    |

| U <sub>6</sub>                      | MC145484DW | N/A       | N/A    | CDC, CFB                                               | 4.7μF       | 20%                       | 20V    |

| R <sub>RT</sub> , R <sub>TRAP</sub> | 20kΩ       | 1%        | 0.10W  | CPS1, CPS2,<br>CPS3, CPS4,<br>CPS5                     | 0.1μF       | 20%                       | 100V   |

| R <sub>SH</sub>                     | 49.9kΩ     | 1%        | 0.10W  | C2, C3, C4, C5, C6                                     | 0.1μF       | 20%                       | 20V    |

| R <sub>IL</sub>                     | 71.5kΩ     | 1%        | 0.10W  | CR3                                                    | DL4003CT-ND | N/A                       | N/A    |

| R <sub>TA</sub>                     | 100Ω       | 1%        | 0.25W  | DTA                                                    | BAS21ZXCT   | N/A                       | N/A    |

| R <sub>S</sub>                      | 66.5kΩ     | 1%        | 0.10W  | CR1, CR2                                               | LN1251C     | N/A                       | N/A    |

| R <sub>P</sub>                      | 0Ω         | 1%        | 0.10W  | R4                                                     | 44.2kΩ      | 1%                        | 0.10W  |

| R <sub>1</sub> , R <sub>2</sub>     | 499Ω       | 1%        | 0.10W  | RTL                                                    | 17.8kΩ      | 1%                        | 0.10W  |

| R <sub>IN</sub>                     | 66.5kΩ     | 1%        | 0.10W  |                                                        |             |                           |        |

## ISL5585XEVAL1 Mechanical Component List

| COMPONENT                         | VALUE         | TOLERANCE | RATING | COMPONENT                                                | VALUE         | TOLERANCE | RATING |

|-----------------------------------|---------------|-----------|--------|----------------------------------------------------------|---------------|-----------|--------|

| U <sub>1</sub> - Socket           | 822271-1      | N/A       | N/A    | J14, J15                                                 | 10 Pin Header | N/A       | N/A    |

| U <sub>6</sub> Socket             | IC51-0202-347 | N/A       | N/A    | J2, J3, J4                                               | 39F893        | N/A       | N/A    |

| J5, J6                            | 43045-1000    | N/A       | N/A    | JP5, JP10                                                | 3 Pin Header  | N/A       | N/A    |

| J1                                | 555165-1      | N/A       | N/A    | JP1, JP2, JP3, JP4,<br>JP6, JP7, JP8, JP9,<br>JP11, JP12 | 1 Pin Header  |           |        |

| J7, J8, J9, J10, J11,<br>J12, J13 | CBJR20        | N/A       | N/A    | S1, S2, S3, S4, S5,<br>S6                                | 65F1681       | N/A       | N/A    |

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com